Das neueste Update für Intels LLVM-Compiler fügt Unterstützung für Xe-HPCVG-Grafikgeräte und Ponte Vecchio VG, eine Variante von Ponte Vecchio (via Coelacanth’s Dream), hinzu. Die neue VG-Variante sowohl der Xe-HPC-Architektur als auch von Ponte Vecchio verfügt über deaktivierte DPAS-Anweisungen (Dot Product Accumulate Systolic), die für KI-Workloads entscheidend sind und normalerweise durch Xe Matrix Extension (XMX)-Einheiten beschleunigt werden.

In vielerlei Hinsicht unterscheidet sich Xe-HPCVG nicht von Xe-HPC: Es verfügt nach wie vor über 128 KB gemeinsam genutzten lokalen Speicher, FP64-Berechnungen mit doppelter Genauigkeit und BF16-Unterstützung mit halber Genauigkeit. Der Hauptunterschied ist jedoch das ausdrückliche Fehlen von DPAS-Befehlen, bei denen es sich um AI-beschleunigte Versionen von Halbpräzisionsbefehlen wie BF16, FP16 und INT8 handelt. Diese Befehle sind für eine gute Leistung bei KI und maschinellem Lernen entscheidend.

Die Tatsache, dass eine Version des Ponte Vecchio ohne DPAS-Befehle ausgeliefert wird, ist definitiv merkwürdig, da der Chip hauptsächlich für KI-Workloads gedacht ist. Das Fehlen von DPAS-Befehlen bedeutet, dass es auf dieser VG-Variante des Ponte Vecchio keine funktionierenden XMX-Einheiten gibt. Es ist schwer vorstellbar, dass Intel eine neue Version des Ponte Vecchio herstellt, um eines seiner Hauptmerkmale zu entfernen. Es könnte also sein, dass Intel die Ponte Vecchio-Chips mit defekten XMX-Einheiten für eine kommende GPU wiederverwendet.

Es ist auch unklar, was das „VG“ bedeutet, obwohl es für etwas wie das „SDV“ in Ponte Vecchio SDV stehen könnte (was für Software Development Vehicle steht). Leider gibt uns das Update nur sehr wenig Anhaltspunkte, da es sich hauptsächlich um die Entfernung der spezifischen Unterstützung für DPAS-Anweisungen und nicht viel mehr handelt.

Wenn Intel eine XMX-freie Version von Ponte Vecchio auf den Markt bringen will, sind wir uns nicht sicher, für welchen Markt sie gedacht ist. XMX-Einheiten, wie Nvidias Tensor-Kerne, haben sich als sehr wichtig für KI-Workloads erwiesen. Ohne diese bleiben dem Ponte Vecchio VG nur FP64 und plattformbezogene Funktionen. Die FP64-Leistung von 52 TFLOPs ist immer noch beeindruckend und übertrifft Nvidias H100 mit 26 TFLOPs, aber sie liegt weit hinter AMDs MI300X mit 81,7 TFLOPs.

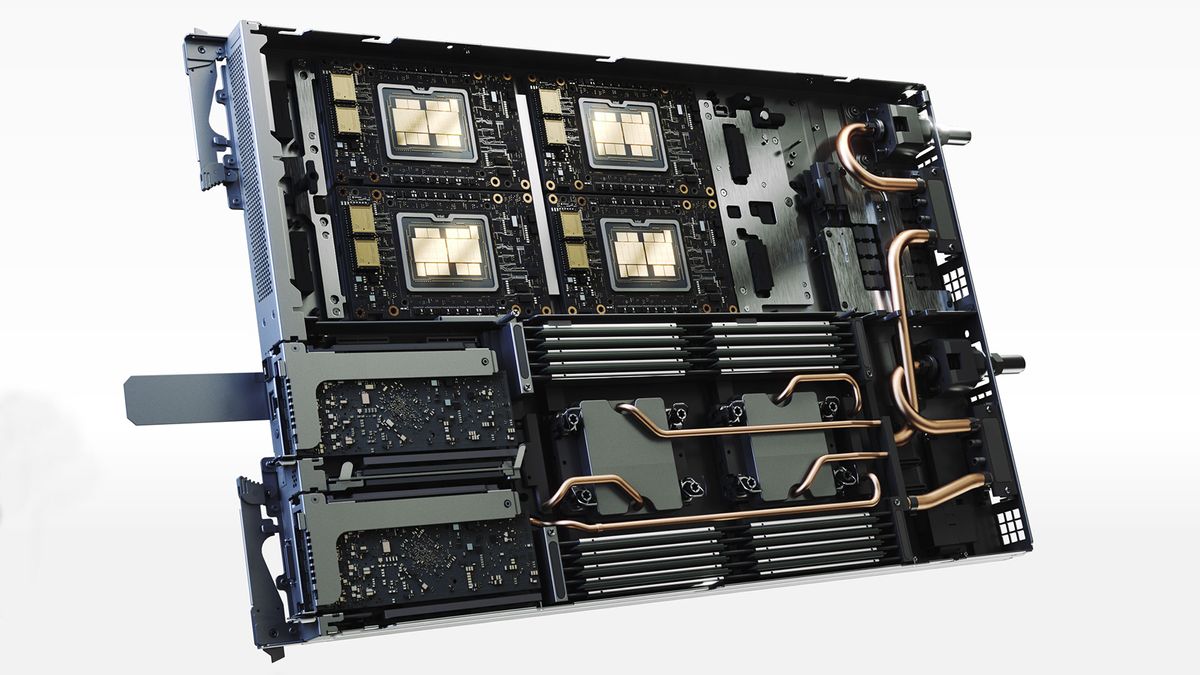

Ponte Vecchio stellt für Intel eine massive Investition in Chip-Stacking und EMIB dar. Die Gesamtlösung besteht aus 47 verschiedenen „Kacheln“ (Chips), die auf verschiedenen Prozessknoten von Intel und TSMC hergestellt werden. Die XMX-Befehle sind ein integraler Bestandteil der Compute Tiles, so dass es unwahrscheinlich ist, dass Defekte nur die XMX-Teile der Chips betreffen. Wahrscheinlicher ist, dass es sich um eine absichtliche Entscheidung von Intel handelt, diese Funktion zu deaktivieren, aber zu welchem Zweck, bleibt unbekannt. Wir werden in Zukunft mehr erfahren, wenn oder falls diese VG-Teile auf den Markt kommen.