Wenn es ein technisches Produkt gibt, bei dem die Skalierung nicht ganz so gut funktioniert, dann ist es DRAM. Dafür gibt es eine Reihe von Gründen, von denen der wichtigste das eigentliche Design der DRAM-Zellen und die Art und Weise ist, wie es mit der Herstellung zusammenhängt.

Laut Lam Research bedeutet das Endergebnis dieser Skalierungsschwierigkeiten jedoch, dass die Forscher im DRAM-Bereich möglicherweise schon in fünf Jahren keine Möglichkeiten mehr haben, die Skalierung der DRAM-Dichte zu erhöhen.

Vor diesem Hintergrund hat Lam Research, ein auf die Entwicklung von Halbleiterschaltungen spezialisiertes Unternehmen, einen Vorschlag für die Entwicklung künftiger DRAM-Produkte veröffentlicht. Und diese Zukunft könnte sehr wohl 3D sein, so dass es scheint, dass Speicherwürfel nicht so weit außerhalb des Bereiches der Möglichkeiten liegen. Nach Angaben des Unternehmens wird es etwa fünf bis acht Jahre dauern, bis ein herstellbarer 3D-DRAM-Baustein entwickelt werden kann, so dass zwischen dem Ende der 2D-DRAM-Skalierung und dem Beginn der 3D-DRAM-Skalierung eine Lücke von etwa drei Jahren klaffen könnte.

Mithilfe der firmeneigenen Software SEMulator3D hat Lam Research mögliche 3D-DRAM-Designs durchgespielt. Der Schwerpunkt lag dabei auf der Lösung von Problemen bei der Skalierung und dem Stapeln von Schichten, der Verkleinerung von Kondensatoren und Transistoren, der Konnektivität zwischen den Zellen und der Anordnung von Durchkontaktierungen (z. B. TSV [Through Silicon Vias] von TSMC, die wir bereits in anderen 3D-Halbleiterdesigns gesehen haben). Schließlich legte das Unternehmen die Prozessanforderungen fest, die die Herstellung des vorgeschlagenen Designs ermöglichen.

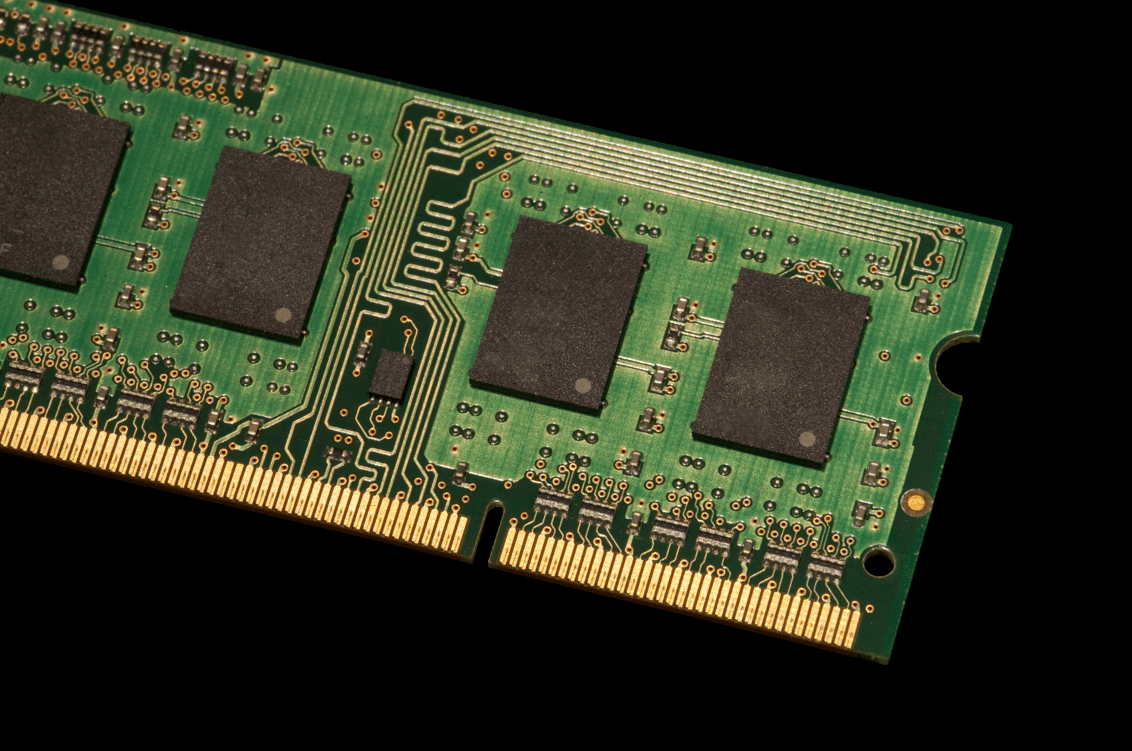

Eine Ansicht der 2D-DRAM-Architektur in vertikaler Ausrichtung, das gleiche Design, das in aktuellen DRAM-Architekturen verwendet wird. Das Kippen und Übereinanderstapeln von Strukturen ist vor allem deshalb nicht praktikabel, weil seitliche Hohlräume geätzt und mit unterschiedlicher seitlicher Tiefe in den aktiven Siliziumbereich gefüllt werden müssen.

Aufgrund der Art und Weise, wie DRAM-Zellen konstruiert sind, ist es nicht möglich, 2D-DRAM-Komponenten einfach auf die Seite zu legen, um sie dann übereinander zu stapeln. Dies liegt daran, dass DRAM-Zellen ein hohes Seitenverhältnis haben (sie sind höher als dick). Um sie auf die Seite zu legen, wären seitliche Ätz- (und Füll-) Fähigkeiten erforderlich, die unsere derzeitigen Kapazitäten übersteigen.

Aber wenn man die Architektur selbst versteht, kann man sie ändern und anpassen und dabei versuchen, die Designbeschränkungen zu umgehen. Das ist jedoch leichter gesagt als getan, und es gibt einen Grund, warum wir noch keinen 3D-DRAM haben.

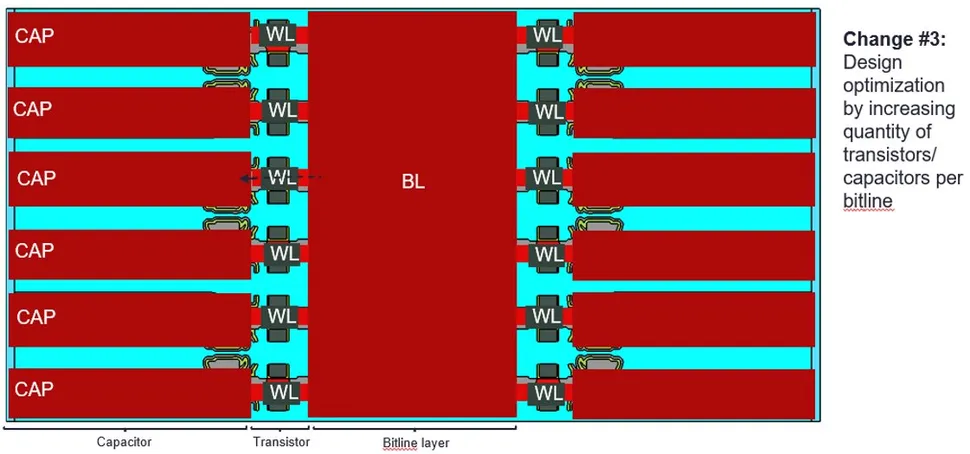

Aktuelle DRAM-Schaltkreisdesigns benötigen im Wesentlichen drei Komponenten: eine Bitleitung (eine leitende Struktur, die Strom einspeist); einen Transistor, der den Stromausgang der Bitleitung empfängt und als Gate dient, das steuert, ob elektrischer Strom in den Schaltkreis fließen (und ihn füllen) kann; und einen Kondensator, in dem der Strom, der durch die Bitleitung und den Transistor fließt, letztendlich in Form eines Bits (0 oder 1) gespeichert wird.

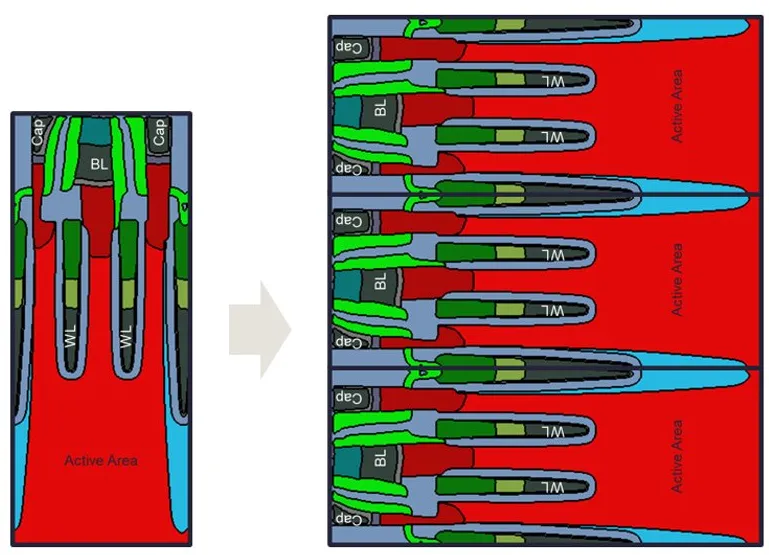

Lam Research wandte einige „Tricks“ beim Chipdesign an, um eine funktionierende Architektur zu erreichen. Zum einen wurde die Bitleitung auf die gegenüberliegende Seite des Transistors verlegt. Da die Bitleitung nicht mehr von einem Kondensator umgeben ist, können mehr Transistoren an die Bitleitung selbst angeschlossen werden, was die Chipdichte erhöht.

Das endgültige DRAM-Zellendesign von Lam Research ermöglicht die Versorgung einer größeren Anzahl von Transistoren über dieselbe Bitleitung, wodurch die Speicherdichte verbessert und das Design gleichzeitig „abgeflacht“ wird, so dass es besser für die 3D-Skalierung geeignet ist.

Um den Gewinn an Flächendichte zu maximieren, hat Lam Research auch einige hochmoderne Transistor-Herstellungstechniken angewandt. Dazu gehören Gate-All-Around (GAA) Forksheet-Designs, die Intel offenbar für die Gating-Technologien der nächsten Generation erforscht. Die von Lam Research vorgeschlagene neu gestaltete DRAM-Architektur kann dann gestapelt werden, wobei Schichten über Schichten des neuen DRAM-Zellendesigns übereinander gelegt werden, und zwar in einem Prozess, der dem von NAND nicht unähnlich ist.

Während die Skalierung bei NAND derzeit bei etwa 232 Schichten liegt, schätzt Lam Research, dass die erste Generation eines 3D-DRAM-Designs wie das eigene nur bis zu 28 gestapelte Schichten nutzen würde. Lam Research schätzt, dass mit den Architekturverbesserungen und zusätzlichen Schichten eine sprunghafte Verbesserung der DRAM-Dichte um zwei Knoten erreicht werden kann, wobei weitere Verbesserungen durch Hinzufügen zusätzlicher Schichten zum DRAM-Wolkenkratzer möglich sind. Wie bei anderen Fertigungstechnologien üblich, wird ein Via-Array (die Technologie, die dem TSV von TSMC zugrunde liegt) verwendet, um die einzelnen Schichten miteinander zu verbinden.